## **Flying Probe Testing**

# **PCBA Design for Testability**

Design for Testability of Printed Circuit Board Assemblies

## **Test Engineer's Handbook**

**SPEA SpA** 16, Via Torino 10088 Volpiano - Italy

Tel.: + 39 011 9825 400 Fax: + 39 011 9825 405 E-mail: info@spea.com Web: www.spea.com

Code: 81110142.067 – Version 7 Original instructions

## Contents

| Rev  | visions | 5                                                        | 1  |

|------|---------|----------------------------------------------------------|----|

| Intr | oduct   | ion                                                      | 2  |

| 1.   | Testi   | ng with Flying Probe tester                              | 4  |

|      | 1.1     | Types of manufacturing processes for PCBA                |    |

|      | 1.2     | Types of test for PCBA                                   |    |

| 2.   | Elect   | rical design rules                                       | 5  |

|      | 2.1     | Contact points                                           | 5  |

|      |         | 2.1.1 Minimum test point dimensions VS System capability |    |

|      |         | 2.1.2 Rules for the placement of test points             |    |

|      |         | 2.1.3 Distance of contact points from high components    |    |

|      |         | 2.1.4 Priority of the contact points                     |    |

|      |         | 2.1.5 Test Pad                                           |    |

|      |         | 2.1.6 Pad10                                              |    |

|      |         | 2.1.7 Soldering Pad                                      | 11 |

|      |         | 2.1.7.1 Component placement error                        |    |

|      |         | 2.1.7.2 Types of soldering pads                          |    |

|      |         | 2.1.8 Via 14                                             |    |

|      |         | 2.1.8.1 Via geometry                                     |    |

|      |         | 2.1.8.2 Types of Vias                                    | 15 |

|      |         | 2.1.8.3 Via identification                               |    |

|      |         | 2.1.9 TH Pin                                             | 17 |

|      | 2.2     | Circuit configurations                                   |    |

|      |         | 2.2.1 Initialization circuits and electrical constraints |    |

|      |         | 2.2.2 Frequency measurements                             |    |

|      |         | 2.2.3 Designing for High and Low signal constraints      |    |

| 3.   | Mech    | nanical design rules                                     | 22 |

|      | 3.1     | Fiducial                                                 |    |

|      |         | 3.1.1 Alignment Fiducials on panel of boards             | 2/ |

|      |         | 3.1.2 Fiducial Area                                      |    |

|      | 3.2     | Fiducial for board presence check                        |    |

|      | 3.3     | Transportability                                         |    |

|      | 3.4     | Board dimension                                          |    |

|      | 3.5     | Panel of boards                                          |    |

|      | 3.6     | Warped boards                                            |    |

| 4.   | Desi    | gn rules to enhance test performance                     | 36 |

|      | 4.1     | Fixturing and wiring Series 1 and Series 2 systems       |    |

|      |         | 4.1.1 Fixturing on panel of boards                       |    |

|      |         | 4.1.1.1 Mechanical characteristics for panel centering   |    |

|      |         | 4.1.2 Cabling on panel of boards                         |    |

|      |         |                                                          |    |

| 4.2 | Open pi                                                      | n test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                                                         |

|-----|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|     | 4.2.1                                                        | Electro scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                                         |

|     | 4.2.2                                                        | Junction scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                                                         |

| 4.3 | 2D Code                                                      | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                         |

| 4.4 | Multi Pro                                                    | be Unit (4080)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                         |

|     | 4.4.1<br>4.4.<br>4.4.<br>4.4.<br>4.4.<br>4.4.<br>4.4.<br>4.4 | 1.2       Pads design         1.3       Components height         1.4       Working area         1.5       Placement inside UUT         1.6       MPU vs other test points         1.7       Simultaneously MPU positioning         1.8       MPU on panel of boards         Multi       Probe on system bottom side         2.1       Head 5-8 pinout         2.2       Pads design         2.3       Components height         2.4       Working area         2.5       Placement inside UUT         2.6       MPU vs other test points | 47<br>48<br>49<br>50<br>51<br>52<br>53<br>53<br>53<br>55<br>55<br>56<br>57 |

| 4.5 | 4.4.2                                                        | 2.8 MPU on panel of boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|     | 4.5.1<br>4.5.2                                               | Pins accessibility<br>Height of the components around the led                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60<br>61                                                                   |

| 4.6 | Side Dev                                                     | vice Interface (4080)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                         |

|     | 4.6.1<br>4.6.2<br>4.6.3<br>4.6.4                             | Mechanical design of the pads<br>Electrical connections<br>Electrical connections on the board<br>Electrical constraints                                                                                                                                                                                                                                                                                                                                                                                                                  | 64<br>65                                                                   |

| 4.7 | Program                                                      | mable components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                         |

|     | 4.7.1<br>4.7.2<br>4.7.3                                      | Pre-requisites for accessibility and constraints<br>OTP components<br>Programming of several components connected to each other                                                                                                                                                                                                                                                                                                                                                                                                           | 68<br>68                                                                   |

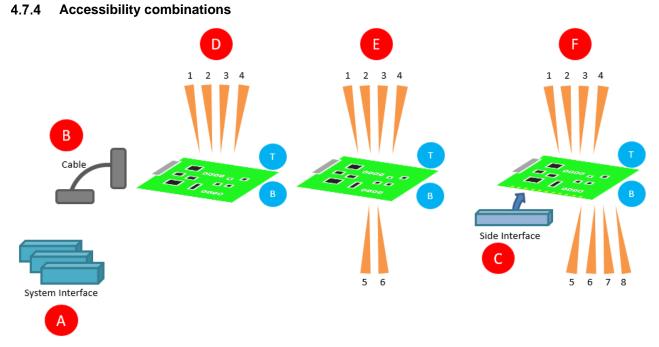

|     | 4.7.4                                                        | Accessibility combinations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69                                                                         |

## Revisions

| Version | Date     | Comments                                            |

|---------|----------|-----------------------------------------------------|

| 4       | 15.11.16 | General review                                      |

| 5       | 15.12.16 | Added chapters:                                     |

|         |          | Via identification                                  |

|         |          | Junction Scan                                       |

|         |          | 2D Code                                             |

|         |          | Updated chapters                                    |

|         |          | TH Pin                                              |

|         |          | Panel of boards                                     |

|         |          | Warped boards                                       |

| 6       | 06.10.17 | Added chapter:                                      |

|         |          | Multi Probe Unit (4080)                             |

| 7       | 12.06.18 | Modified chapter:                                   |

|         |          | Multi Probe Unit (4080)                             |

|         |          | Added chapter:                                      |

|         |          | <ul> <li>Measurement of light parameters</li> </ul> |

|         |          | Side device interface (4080)                        |

|         |          | Programmable components                             |

## Introduction

The Design for Testing or Design for Testability (DFT) consists of a series of rules for the design of electronic boards in order to:

- 1. Ensure the testability of each mounted component (In-Circuit Test);

- 2. Simplify the testability of the functions (Functional Test);

- 3. Allow for programming of the programmable components (On-Board Programming);

- 4. Make the automatic test generation possible

- 5. Make the In-Line transport of the board possible

The purpose of the production testing (*Manufacturing Test*) of an electronic board is to ensure that there are no defects, which may cause malfunction of the circuits or early on field failure of the mounted components. In addition, the purpose of Manufacturing Test is the production process control. This prevents the production line to start producing defects as the time goes by.

Each net of the circuit needs available Testpoints in order to allow the complete testing of each component and the automatic generation of the test program (ATPG).

This is to ensure the maximum failures coverage and the minimum cost of testing.

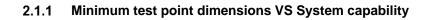

The flying probe tester can contact very small testpoints but it is recommended to use, where possible, the recommended size in order to increase the speed of contacting and to reduce the testing time.

In summary, this document contains:

- 1. the electrical design rules

- 2. the mechanical design rules

- 3. the design rules to increase of the testing performance

• Legend

Recommended requirement

Economic advantage to save on the cost of testing.

Advantage in terms of test program development time.

Reference in SPEA documentation for detailed information.

Caution

### • Abbreviations

| $\triangleright$ | FP   | Flying Probe Tester            |

|------------------|------|--------------------------------|

| $\triangleright$ | UUT  | Unit under test                |

| $\succ$          | TPGM | Test program                   |

| $\triangleright$ | TH   | Through hole                   |

| $\triangleright$ | SMD  | Surface Mounted Device         |

| $\triangleright$ | OBP  | On Board Programming           |

| $\succ$          | PCB  | Printed Circuit Board          |

| $\triangleright$ | PCBA | Printed Circuit Board Assembly |

| ≻                | QC   | Quality Control                |

#### **Testing with Flying Probe tester** 1.

#### 1.1 Types of manufacturing processes for PCBA

The manufacturing process of the board to be tested will affect the choice of the design strategy of the board itself.

For this reason, it is essential to take the manufacturing process into account when adopting the Design For Testability rules.

Manufacturing processes:

- 1. Hi-Volume Manufacturing Test

- 2. Low-Med Volume Manufacturing Test

- 3. Prototype Test

- 4. Quality Control (QC) Process Test

- 5. SMD Line Set-Up Check

- 6. Repair Loop

- 7. Field Repair

## 1.2 Types of test for PCBA

The types of tests that will be executed on the board are also fundamental in the design strategy of the card.

Types of test:

- 1. In-Circuit Test Power Off

- 2. In-Circuit Test Power On

- 3. Short circuit test

- 4. Power supply test

- 5. Open pin test

- 6. Nodal impedance test

- 7. Nodal voltage test

- Insulation test

On-Board Programming

- 10. Build-In-Self-Test

- 11. Boundary Scan

- 12. Functional test

- 13. Optical test

- 14. Laser test

- 15. Light test

- 16. Nodal waveform test

## 2. Electrical design rules

## 2.1 Contact points

The **contact point** is a contactable surface where it is possible to place a **Testpoint**.

A contact point can be made on any contactable surface (VIA, SMD Pad, Pad TH, Test Pad, etc.) with the following features:

- 1. Flatness

- 2. Conductivity

- 3. Minimum dimensions

- 4. Accessibility

- 5. Located on the same level of PCB (recommended)

The testpoints are useful to contact the nets of the board under test in order to test:

- 1. The connected components

- 2. The absence of defects (short circuits, broken tracks, impedances)

- 3. The expected features

Picture 1 - Relationship between size of the contact, test performance and system capability

### 2.1.2 Rules for the placement of test points

| No. | Net Type      | Minimum Test points net | Recommended Test point per net |

|-----|---------------|-------------------------|--------------------------------|

| 1   | Analog        | 1                       | >1                             |

| 2   | Digital       | 1                       | >1                             |

| 3   | Not Connected | 1                       | 1                              |

| 4   | Power         | 2                       | >2                             |

| 5   | Ground        | 2                       | >10                            |

| 6   | Power supply  | 2                       | >10                            |

Table 1 – Quantity of test points per type of net

### 2.1.3 Distance of contact points from high components

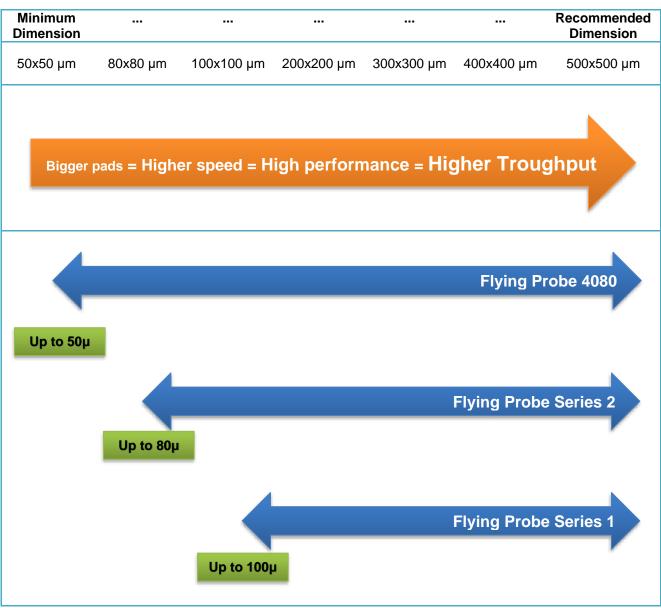

Components higher than 7mm, generate shaded areas that can affect the complete accessibility of the contact points in their surroundings. All the probes of the Flying Probe are affected by this concept.

This chapter suggests the rule to be used to obtain the maximum accessibility of the contact points by all the Flying Probe probes.

Applicability is valid for components up to 28mm in height.

In the case of components with a height between 28mm and 55mm, is required a specific study that takes care of the following aspects:

- Flying prove model (4 probes, 6 probes, 8 probes, manual, in-line, ...);

- Open Pin Electro Scan present on axis;

- Light Meter (Led Color Sensor) present on axis.

Picture 2 – Maximum accessibility calculation

| Symbol                                                                                    | Description                                                                                                             |  |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| h                                                                                         | Component nominal height (max 28mm).                                                                                    |  |

| h'                                                                                        | 3mm margin (to be considered for h> 5.5mm).                                                                             |  |

| α                                                                                         | 16° (is considered the axis with greater angle on 40xx S2).<br>13° (is considered the axis with greater angle on 4080). |  |

| x                                                                                         | Distance "margin - center of contact point" due to the projection of the nail.                                          |  |

| x'                                                                                        | Margin of 2.5mm.                                                                                                        |  |

| D Clearance distance from "test point or contact poin positioned beyond the D dimension). |                                                                                                                         |  |

|                                                                                           | Table 2 – Parameters                                                                                                    |  |

7

## 2.1.4 Priority of the contact points

| Priority | ority Type Description                                                                                                              |                                                                                                                               | Drawing |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|

| 1        | Test Pad                                                                                                                            | Point of contact on the PCB arranged exclusively for testing and non-functional to the board.                                 | -       |

| 2        | 2 Pad Point of contact on the PCB arranged as electrical requirement of the board (e.g. not mounted component, track terminations). |                                                                                                                               |         |

| 3        | Via                                                                                                                                 | Through hole connecting different layers of the PCB.                                                                          | -0-     |

| 4        | Pin TH                                                                                                                              | Contact point created on the welding of a through hole component pin (mounted on one side and contactable on the other side). |         |

| 5        | Soldering Pad                                                                                                                       | Contact point of the printed circuit with welded SMD components or of integrated circuit pins welded on it.                   | <b></b> |

Table 3 - Priority of the contact points

## 2.1.5 Test Pad

The Test Pads are the preferred contact points of the printed circuit, designed exclusively for testing and non-functional to the board.

The Test Pads allow contacting each net of the PCB, preventing the need to contact less than optimal contact points. It is therefore recommended to have at least a one test pad per net.

| No. | Туре                   | Layout | Example | Minimum<br>dimension | Recommended dimension | Contacting capability |

|-----|------------------------|--------|---------|----------------------|-----------------------|-----------------------|

| 1   | Round                  | ┥      | CANTEL  | Ø 70 µm              | Ø 500 µm              | QUALIFIED             |

|     |                        |        |         | Ø 70 µm              | Ø 500 µm              | QUALIFIED             |

| 2   | Square                 | -4     |         | 70 x 70 μm           | 500 x 500 μm          |                       |

|     |                        |        |         | 70 x 70 μm           | 500 x 500 μm          | QUALIFIED             |

| 3   | Embedded<br>in a trace |        | -       | 70 x 70 µm           | 500 x 500 µm          | QUALIFIED             |

| 4   | Half round             | -      | -       | 70 x 70 μm           | 500 x 500 μm          | QUALIFIED             |

| 5   | Triangle               |        | -       | 70 x 70 μm           | 500 x 500 µm          | QUALIFIED             |

Table 4 – Test Pad

## 2.1.6 Pad

Point of contact on the PCB arranged as electrical requirement of the board, but that can also be contacted for testing purposes.

| No. | Туре              | Layout | Example | Minimum<br>dimension | Recommended dimension | Contacting capability |

|-----|-------------------|--------|---------|----------------------|-----------------------|-----------------------|

| 1   | SMD<br>components |        | C504    | 70 x 70 µm           | 500 x 500 μm          | QUALIFIED             |

|     |                   |        |         |                      |                       |                       |

Table 5 – Pad

## 2.1.7 Soldering Pad

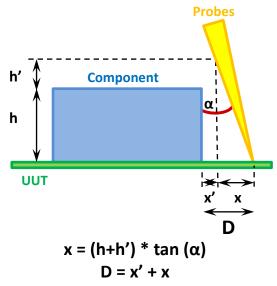

The soldering pad is the whole surface of the pad where the SMD component pin will be welded.

The area remaining after welding the SMD component pin can be used as a contact point:

## 2.1.7.1 Component placement error

The placement error is the positioning tolerance of the pick and place machine when mounting the component.

Consider the following during the board design process:

- This tolerance reduces the size of the contact point according to the formula in figure.

- The designer must consider this tolerance during the board design.

- The mounting tolerance is shown in the datasheet of the machine used for the manufacturing of the board.

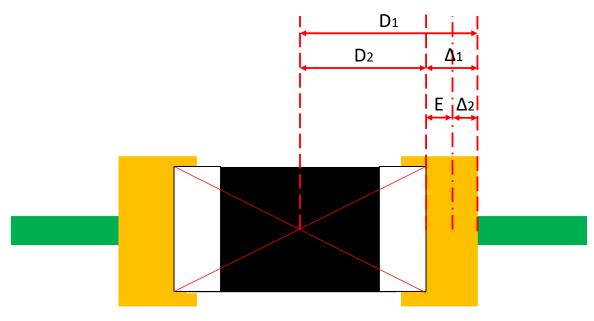

$\Delta_1 = D_1 - D_2$  Size of the pad without placement error

$\Delta_2 = D_1 - D_2 - E$  Size of the pad with placement error

Picture 3 – Example of placement error reducing the contact point

## 2.1.7.2 Types of soldering pads

| No. | Туре              | Layout    | Example | Minimum<br>dimension | Recommended dimension | Contacting capability |

|-----|-------------------|-----------|---------|----------------------|-----------------------|-----------------------|

|     |                   |           | C SCW   | 70 x 70 μm           | 500 x 500 μm          | QUALIFIED             |

| 1   | SMD Device<br>pin |           |         | 70 x 70 µm           | 500 x 500 μm          | QUALIFIED             |

|     | <b>b</b>          |           |         | 70 x 70 µm           | 500 x 500 μm          |                       |

|     | SMD IC pin        | MD IC pin |         | 70 x 70 µm           | 500 x 500 µm          | QUALIFIED             |

|     |                   |           |         | 70 x 70 μm           | 500 x 500 μm          | QUALIFIED             |

| 2   |                   |           |         | 70 x 70 µm           | 500 x 500 μm          |                       |

|     |                   |           |         | 70 x 70 μm           | 500 x 500 μm          | QUALIFIED             |

$^{\ast}$  The minimum pad must include the possible placement error. See dedicated chapter.

Table 6 – Soldering pads

## 2.1.8 Via

Vias are through holes that connect the different layers of the PCB.

A contactable via must not be covered with insulating material and adhere to the mechanical properties below.

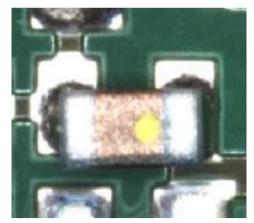

### 2.1.8.1 Via geometry

The geometry of the via should be designed in function of the number contactable and available vias for each net of the board.

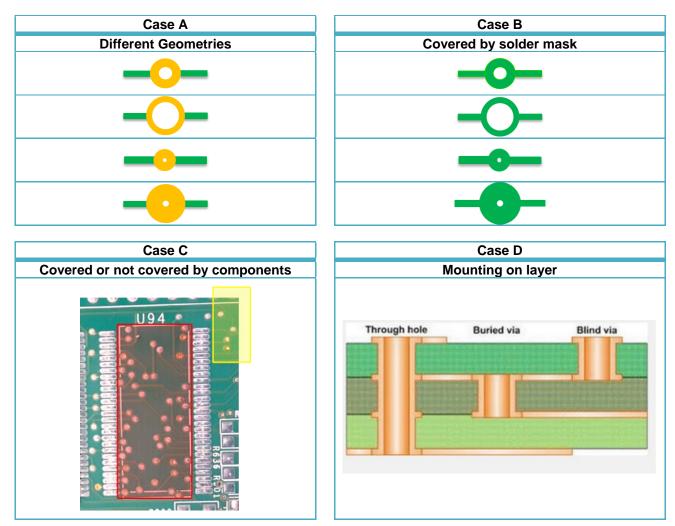

The following table shows the contact area to design on vias to make them contactable:

Table 7 – Contacting areas on via

## 2.1.8.2 Types of Vias

| No. | Туре                               | Layout | Example | Contacting Capability |

|-----|------------------------------------|--------|---------|-----------------------|

| 1   | Round through hole                 | -0     |         | QUALIFIED             |

| 2   | Square or rectangular through hole | -0-    | -       | QUALIFIED             |

| 3   | Through hole followed by pad       | -0     |         | QUALIFIED             |

| 4   | Blind round                        | -0-    |         | QUALIFIED             |

| 5   | Blind square / rectangle           | -0-    | -       |                       |

| 6   | Coated                             | -0-    | 9 0 8   | NOT QUALIFIED         |

Table 8 – Via

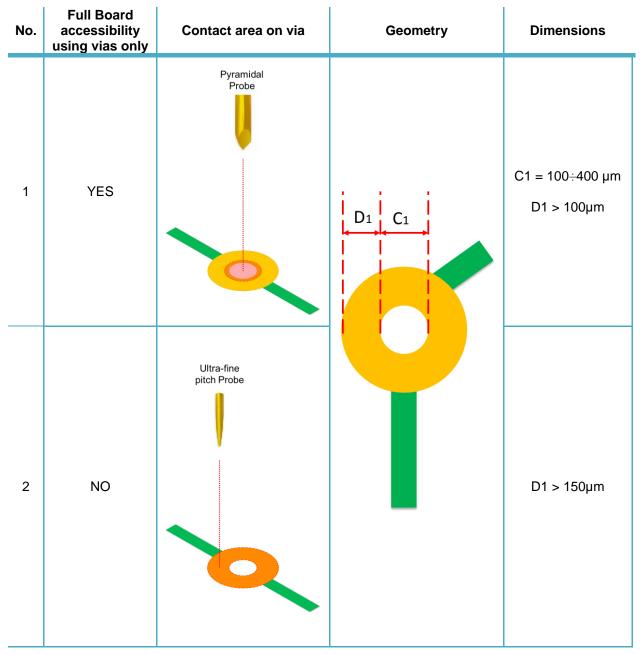

### 2.1.8.3 Via identification

The vias may differ in the following characteristics:

- A. Different Geometries

- B. Covered by solder mask

- C. Covered or not covered by components

- D. Mounting on layer

Depending on the characteristics of the vias on the board to be designed, the vias must be identified with a different part number for each case so they can be used in a simple and effective way during the development of the test program.

Cases

## 2.1.9 TH Pin

A Through Hole (TH) Pin is a pin of vertical mounting axial components, mounted on one side of the board and accessible on the other.

The typical pitch of TH components is 2.54 mm.

The following table shows the contact area to design to allow touching on TH Pins:

| No. | Туре                                         | Example | Contact point on TH pin   | Geometry | Contacting<br>Capability |

|-----|----------------------------------------------|---------|---------------------------|----------|--------------------------|

| 1   | Not mounted<br>component                     |         | Ultra-fine<br>pitch Probe | D1 C1    | QUALIFIED                |

| 2   | Mounted<br>component                         |         | Ultra-fine<br>pitch Probe | -        | QUALIFIED                |

|     |                                              |         | Greasy welding            | -        | NOT<br>QUALIFIED         |

| 3   | Not mounted<br>component with<br>tinned hole |         | Ultra-fine<br>pitch Probe | -        |                          |

Table 10 – Contact point on TH pin

## 2.2 Circuit configurations

An electronic board can encompass particular circuit functions which, when designed under ideal condition, can influence the coverage of the test program developed on FP.

The suggestions in the following chapters point to define an ideal route to making the board suitable not only for classic In-Circuit test, but also for functional test, devices programming, power-on tests etc.

#### 2.2.1 Initialization circuits and electrical constraints

Some signals of the UUT may have to assume a certain state during a certain type of electrical testing. This state can be decisive for their operation and may need to be configured generically before starting the test (In-Circuit, functional, programming, etc ...).

Examples of typical initialization circuits or electrical constraints:

- 1) Reset circuits

- 2) Constraints between grounds or power supplies

- 3) Active high constraints

- 4) Active low constraints

Provide for accessibility of the constraints through the following contact points:

- 1) Test Pad

- 2) Pad

- 3) Soldering Pad

- 4) Via

- 5) Connector

Avoid having a constrained signal useful for the test set only between two components with BGA technology.

In this case, such a signal can never be contacted to be tested.

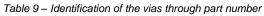

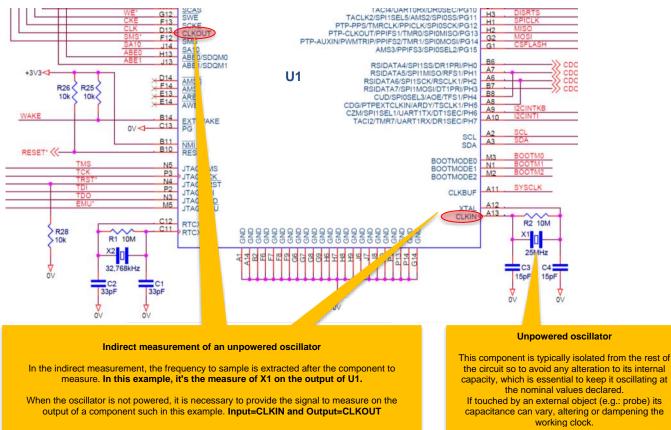

#### 2.2.2 Frequency measurements

The FP is able to execute frequency measurements through the probes thanks to the electronics mounted on the axes themselves.

Two types of measurement exist:

- Direct measurement: executed at the output of the component generating the frequency itself. It can be applied to measure signals not affected by the use of any measurement probe (e.g.: powered oscillators).

- Indirect measurement: executed after the component generating the frequency, therefore on another component.

To measure a quartz, design the board so to have a downstream circuit where for the application of

To measure a quartz, design the board so to have a downstream circuit where for the application of this measurement mode.

Example

•

Picture 4 – Example of an indirect measurement of an unpowered oscillator.

Picture 5 – Example an indirect measurement of the circuit oscillation

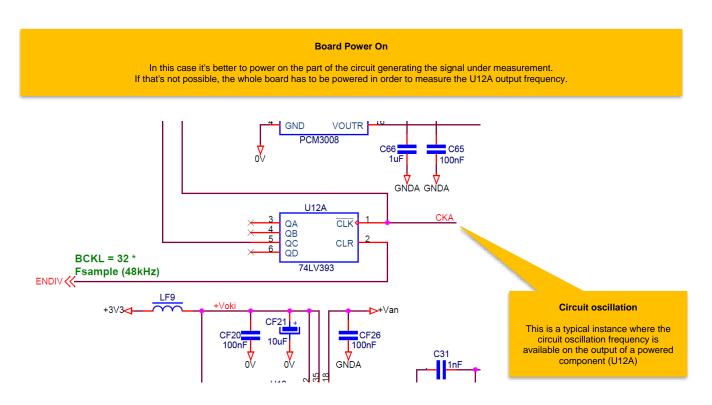

Arranging a pin on the output of a component to measure the clock of the board allows increasing the test coverage on FP, saving on the setup of an eventual functional test.

Designing all the necessary points to measure an oscillation (Power supply, GND and Output) on the same side of the board allows simplifying and speeding up the implementation of a test in an FP program.

Picture 6 – Probes involved in a frequency measure

### 2.2.3 Designing for High and Low signal constraints

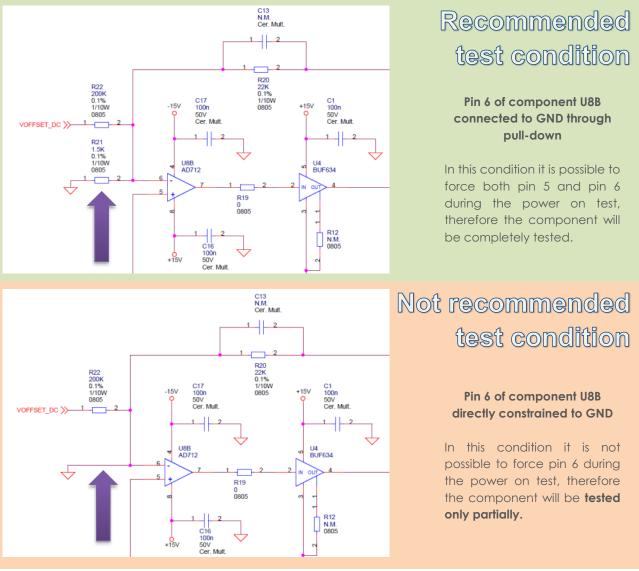

The FP test program can include Power On tests to verify the correct functioning of the analog and digital integrated circuits. On some of the pins of these components, the level of the signal can be constrained to high (e.g.: VCC) or low (e.g.: GND) due to electrical reasons. Fig. 2.1.3.a shows two methods to design Low signals constraints.

When aiming to increase the test coverage through the power on test, it's useful to arrange pull-up or pulldown resistors for the constrain of high and low signals, thus helping to enhance the test performance.

By designing pull-up and pull-down resistors to constrain signals to high or low, it's in fact possible to execute the power on tests by forcing all the inputs of the component to be tested (which would be impossible to do if the pin had been directly constrained through GND or VCC).

Picture 7 - Example of design of a signal constrained to GND.

Designing pull-up or pull-down resistors increases the tests applicable to the integrated circuit, consequently improving its test coverage.

## 3. Mechanical design rules

## 3.1 Fiducial

Board fiducials are elements designed to allow to recognize the UUT orientation inside the test area.

### • Characteristics

| No. | Characteristic                                                 | Requirement |

|-----|----------------------------------------------------------------|-------------|

| 1   | Designed on CAD                                                | RECOMMENDED |

| 2   | Not tin-plated                                                 | RECOMMENDED |

| 3   | Not covered by solder mask                                     | RECOMMENDED |

| 4   | Surrounding area free of copper traces or screen-printed signs | MINIMUM     |

| 5   | Surrounding area free of similar components                    | MINIMUM     |

| 6   | (Asymmetrically) placed on the corners of the board            | ΜΙΝΙΜυΜ     |

| 7   | Placed both on top and of bottom of the board                  | RECOMMENDED |

| 8   | Placed as externally as possible                               | ΜΙΝΙΜυΜ     |

| 9   | High-contrast color compared to PCB                            | MINIMUM     |

Table 11 – Fiducial characteristics

• Position on the board

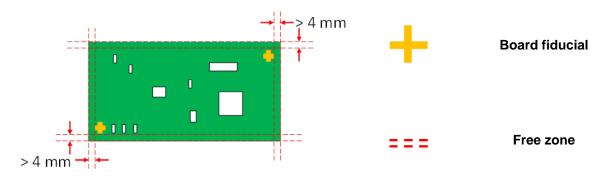

Picture 8 – Fiducial position on the board

• Suitable geometry

| No. | Shape | Minimum<br>Dimension | Recommended<br>Dimension | Catching<br>Capability |

|-----|-------|----------------------|--------------------------|------------------------|

| 1   |       | 500x500 µm           | 800x800 µm               | QUALIFIED              |

| 2   |       | 500x500 µm           | 800x800 µm               | QUALIFIED              |

| 3   | +     | 500x500 µm           | 800x800 µm               |                        |

| 4   | #     | 500x500 µm           | 800x800 µm               | QUALIFIED              |

| 5   |       | 500x500 µm           | 800x800 µm               | QUALIFIED              |

| 6   |       | 500x500 µm           | 800x800 µm               | QUALIFIED              |

Table 12 – Suitable fiducial geometry

Designing the fiducials according to the criteria in this chapter increases its repeatability during board manufacturing and saves test time. This leads to greater overall throughput.

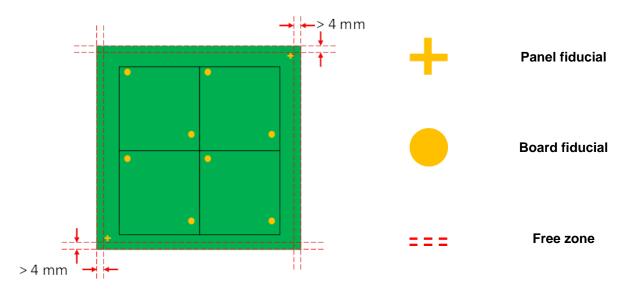

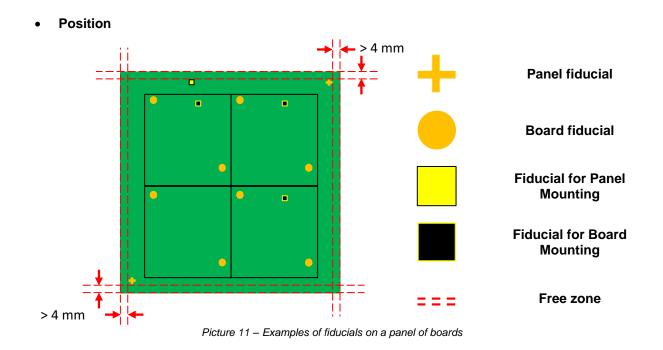

## 3.1.1 Alignment Fiducials on panel of boards

Panel fiducials are elements designed to recognize the orientation of the panel of boards.

The panel fiducials can be used when there is no specific need to use fiducials for the single board. If used in place of the board fiducials, the alignment process will take less time, improving the performance of the test program.

#### Characteristics

Refer to the Fiducial chapter.

#### Position on panel

Picture 9 – Fiducial position on the panel of board

• Geometry

Refer to the Fiducial chapter.

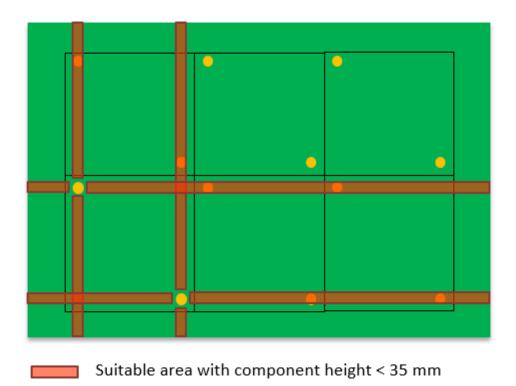

## 3.1.2 Fiducial Area

To make a fiducial accessible for the camera, for any direction of insertion in the test area, it is suggested to respect the areas free of components with height  $\geq$  35mm as shown in the figure.

Picture 10 – Free fiducial area

## 3.2 Fiducial for board presence check

The FP uses a series of reference points to detect if the board of the panel is mounted and consequently has to be tested.

Two types of such points exist:

- 1) General panel fiducial (All Board Mark) Used to determine if 1 or more boards on the panel are not mounted.

- 2) Single board fiducial (Single Board Mark) Used to determine if the board is mounted or not.

- Use on FP

|              | Status    | Detection | Meaning                                       | Following step                   |

|--------------|-----------|-----------|-----------------------------------------------|----------------------------------|

| All board    | Covered   | FAIL      | 1 or more boards<br>are <b>not mounted</b>    | Check the Single<br>Board Mark   |

| mark (A)     | Uncovered | PASS      | All of the boards on panel are <b>mounted</b> | Execute TPGM on all boards       |

| Single board | Covered   | FAIL      | The board<br>is <b>not mounted</b>            | TPGM is not executed             |

| mark (B)     | Uncovered | PASS      | The board is <b>mounted</b>                   | Execute TPGM on the single board |

Table 13 – Board detection according to fiducial used

## • Geometry

Refer to the Fiducial chapter.

Designing fiducials to check the mounting of the boards simplifies the debug operations and saves time during the TPGM development.

## 3.3 Transportability

The shape of the board determines the side used to transport it in the testing machine.

For boards with unusual shape, it is advisable to provide devise methods to simplify transportability in the test equipment.

#### • Characteristics

| Board Typology     | Layout                                                                 | Area without<br>components<br>A | Area without<br>components<br>B |

|--------------------|------------------------------------------------------------------------|---------------------------------|---------------------------------|

| Regularly shaped   | $A = \frac{1}{1}$                                                      | ≥ 4 mm                          | ≥ 4 mm                          |

| Irregularly-shaped |                                                                        | ≥ 4 mm                          | ≥ 4 mm                          |

| Panel of boards    | $A = \frac{1}{B}$ $Table 14 - Transportability and shape of the board$ | ≥ 4 mm                          | ≥ 4 mm                          |

Table 14 – Transportability and shape of the board

#### • Transport of non-transportable board or panel

It is still possible to transport boards not designed according to the recommendations in this chapter with the resulting setup costs.

The following is an example of a transport tray:

Picture 12 – Example of transport tray

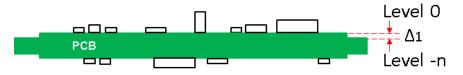

#### • Transport of board with uneven PCB level

The *Level 0* of the PCB corresponds to the surface where the probes will touch. If the card PCB level is uneven in the zone used to clamp it in the test area. It will still be possible to test it by applying suitable precautions in the test program. Nevertheless, where possible, fill the  $\Delta 1$  gap to reduce the development time of the program.

Picture 13 – Side view of a board with uneven PCB level

## 3.4 Board dimension

The board testability on Flying probe system is based on the following characteristics:

- **Operating Test Area** Work area of the FP tools installed on axes.

- **Board Clamp Area** Area for the clamping of the board in the test area.

Refer to the datasheet of own system to know maximum operating areas.

## 3.5 Panel of boards

Panel of boards include more boards and are the best practice to optimize their assembly and test times. The FP is able to manage the test on both single boards and panel of boards. The following table reports the main data:

| BOARD 2  | BOARD 3  | BOARD 4         |

|----------|----------|-----------------|

| BOARD 6  | BOARD 7  | BOARD 8         |

| BOARD 10 | BOARD 11 | BOARD 12        |

|          | BOARD 6  | BOARD 6 BOARD 7 |

Picture 14 – Example of a panel of boards

| Characteristic                                | Notes    |

|-----------------------------------------------|----------|

| Max manageable number of boards per panel     | 256      |

| Rotation management between boards            | Yes      |

| Top/bottom rotation management between boards | Yes      |

| Manageable angles of rotation between boards  | 0-360°   |

| Board fiducials                               | Required |

| Panel fiducials                               | Optional |

| Single board mark for board presence check    | Optional |

Table 15 – Panel of boards characteristics

A panel of boards allows saving on the setup time compared with a single UUT. Consequently, the throughput per hour increases.

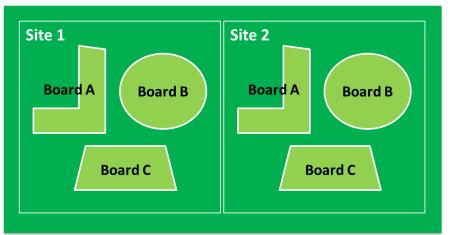

### • Different Part Numbers on panel of boards

To optimize test time, it is possible arrange different boards (with different Part Numbers) on a single panel.

The boards in the following example will be tested using three different test program carried out in sequence.

Picture 15 – Panel of two boards with different Part Numbers

A panel of boards saves on tooling time compared to a single UUT. Consequently, the hourly throughput increases.

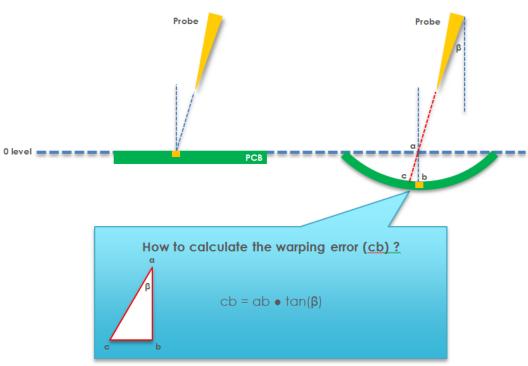

## 3.6 Warped boards

The FP its able to compensate the Z probes travel on the PCB level.

The compensantion its possible by the Laser tool.

Anyway take into account the board warping which could unpredictably affect the contact point as shown below:

Picture 16 - Warping error calculation

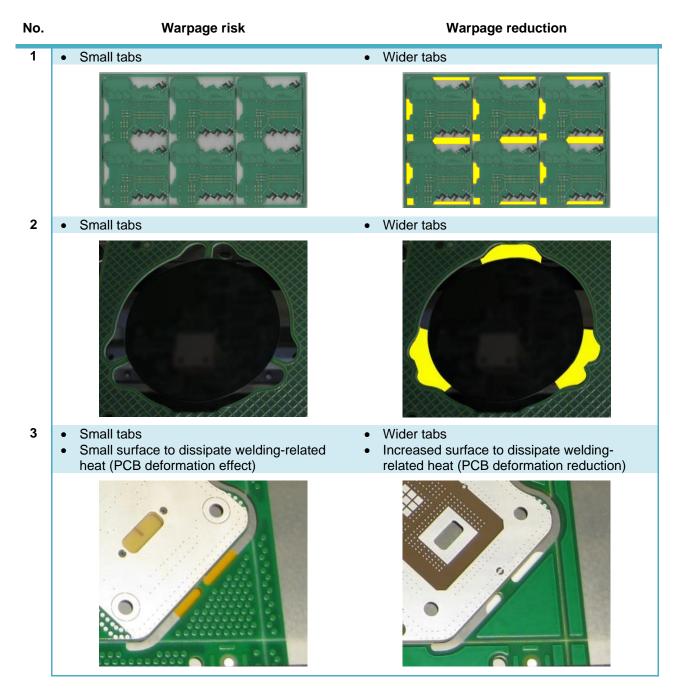

# Warpage reduction

The following table shows some examples of precautions to limit the warping of the panel:

Table 16 - Warpage reduction

#### • Support frame for flexible boards

In case of particularly thin and / or flexible boards, the warping can be compensated by suitable supporting pallet that will affect the cost of testing.

Picture 17 – Support frame for a flexible board

By designing the board to reduce warping, the cost of setup to increase rigidity is reduced.

# 4. Design rules to enhance test performance

# 4.1 Fixturing and wiring Series 1 and Series 2 systems

During the board design process it is possible to arrange the use of stimuli through connector interface instead flying probes to enhance the performance of the test.

The contact points to be touched by those stimuli have to be designed ad-hoc according to the test system used.

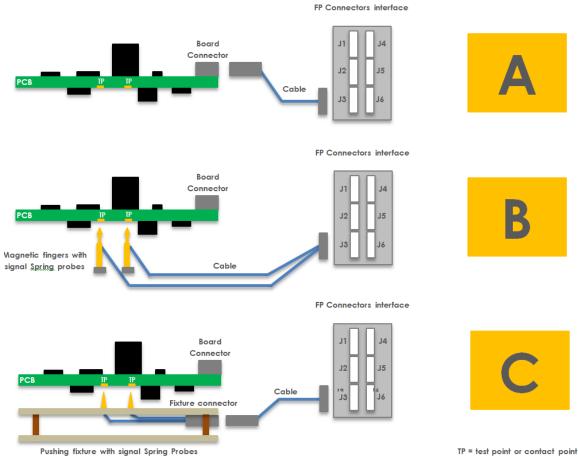

The following picture shows some typical solutions adopted.

Picture 18 - Typical solutions in using external resources

#### Characteristics of the board according to test solution •

| Characteristic                                                    | Solution A<br>Cabling | Solution B<br>Fingers from the bottom side | Solution C                   |

|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------------------------------|

| Applicability on In-Line systems                                  | Yes (1)               | Yes (3)                                    | Yes (3)                      |

| Applicability on Manual systems                                   | Yes                   | Yes                                        | Yes                          |

| Applicability on single boards                                    | Yes                   | Yes                                        | Yes                          |

| Applicability on panels of boards                                 | Yes (2)               | Yes (2)                                    | Yes                          |

| Contact point minimum diameter                                    | -                     | 1.5mm                                      | 0.8mm                        |

| Contacts distribution                                             | -                     | Uniform                                    | Uniform                      |

| Minimum ideal center to center distance<br>between contact points | -                     | 24mm                                       | 2.54mm (100mils)             |

| Minimum center to center distance between contact points          | -                     | 24mm                                       | 1.27mm (50mils)              |

| UUT tooling holes required                                        | -                     | -                                          | 2                            |

| Minimum tooling holes diameter                                    | -                     | -                                          | 3mm                          |

| Cost of setup                                                     | Low                   | Average                                    | High                         |

| Interval of setup on system                                       | At each test          | Once, at production start-up               | Once, at production start-up |

RSL (Removable Shuttle Loader) required

To check according to the kind of test to be executed on the UUT

(3) 4 axes system only

Table 17 - Characteristics of the board according to test solution

## 4.1.1 Fixturing on panel of boards

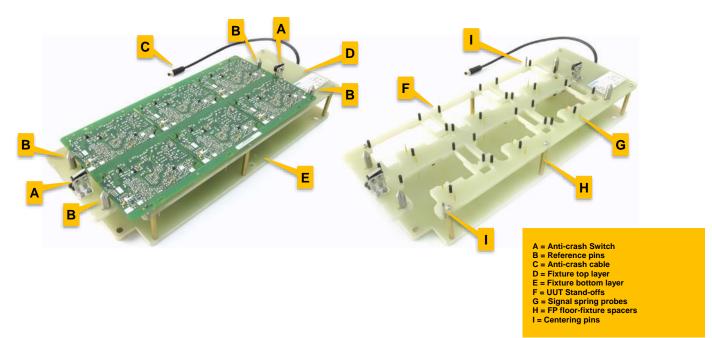

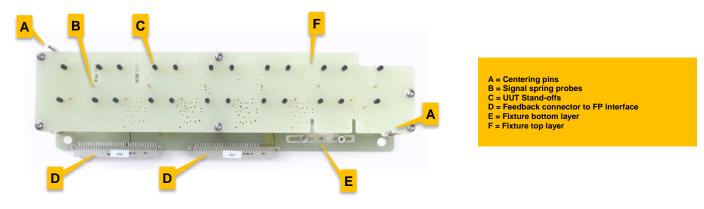

The fixture is a tool to enhance the test performance on 4-probe systems.

• Parts of the fixture

Picture 19 – Example of a 6-board panel fixture for an In-Line system

Picture 20 – Example of a 6-board panel fixture for a Manual system

# 4.1.1.1 Mechanical characteristics for panel centering

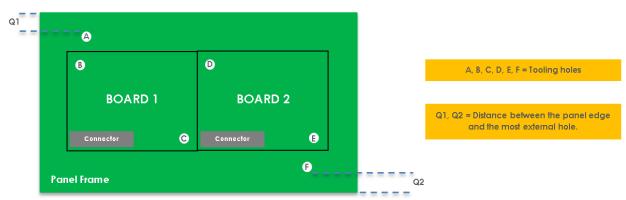

Picture 21 – Example of a 2-board panel to be tested using a fixture

|                                        | Test system model |         |         |               |  |

|----------------------------------------|-------------------|---------|---------|---------------|--|

| Characteristic                         | Shuttle<br>Loader | Manual  | In-Line | Back<br>Panel |  |

| Min diameter A, B, C, D, E, F          |                   | 2mm     | 3mm     | 3mm           |  |

| Minimum Q1, Q2 if used for tooling     | 1mm               | 1mm     | 7.5mm   | 7.5mm         |  |

| Test points distribution on the bottom |                   | uniform |         |               |  |

(1) Do not concentrate the test points on a specific area of the UUT to avoid bending it with the push of the spring probes on the bottom side.

Table 18 – Mechanical characteristics for panel centering

If the UUT mechanical references are suitably designed, it will be possible to save the hours of work necessary for the arranging of particular setups due to the noncompliance with the quotes specified on table.

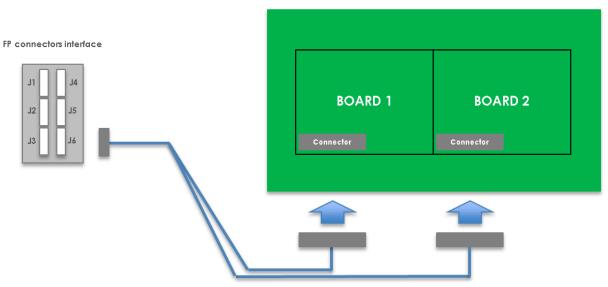

#### 4.1.2 Cabling on panel of boards

Cabling is a tool to enhance the test performance on Flying Probe systems.

When arranging a setup as shown in picture, it is recommended to place the connectors of the external cable according to the following rules:

- 1) On the side with less or none accessibility to the copper tracks (so that the test with FP probes is executed on the opposite side).

- 2) As close as possible to the border of the UUT, in order to avoid the passage of the cable over the components (if the connector is on the same side used for the test).

Picture 22 - Example of setup through cable on a panel of boards

The table below reports the applicability of the solution with cabling on panel of boards sorted by model of system:

|                                             | Test system model\ |        |         |               |

|---------------------------------------------|--------------------|--------|---------|---------------|

| Characteristic                              | Shuttle<br>Loader  | Manual | In-Line | Back<br>Panel |

| Applicability of cabling on panel of boards | Yes                | Yes    | Yes (1) | Yes \(1)      |

(1) RSL (Removable Shuttle Loader) required if available on system tester.

Table 19 – Cabling applicability per system model

# 4.2 Open pin test

The SPEA FP is able to check the components pins welding through a 2 different techniques known as:

- 1. Electro scan

- 2. Junction scan

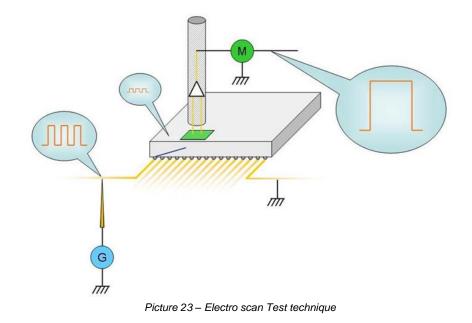

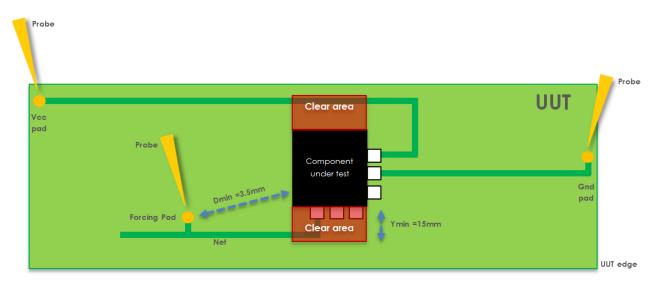

## 4.2.1 Electro scan

The test consists in forcing a signal on the net of the pin under test with a probe; then, with a specific hardware, the electric field emitted by the pin itself is measured through the case of the component under test.

Below, a representation of the test technique.

• Test technique

## Accessibility of the nets connected to the pin under test

Picture 24 – Accessibility of the nets connected to the pin under test

| Characteristic                                                     | Parameter | Value                 |  |  |

|--------------------------------------------------------------------|-----------|-----------------------|--|--|

| Min. distance between the forcing pad to the case of the component | D min     | 3.5 mm                |  |  |

| Clear area suggested where the components height $\leq$ 7mm        | Y min     | 15 mm                 |  |  |

| Component power net accessibility suggested                        | Vcc       | Close to the UUT edge |  |  |

| Component ground net accessibility suggested                       | GND       | Close to the UUT edge |  |  |

Table 20 – Test point accessibility

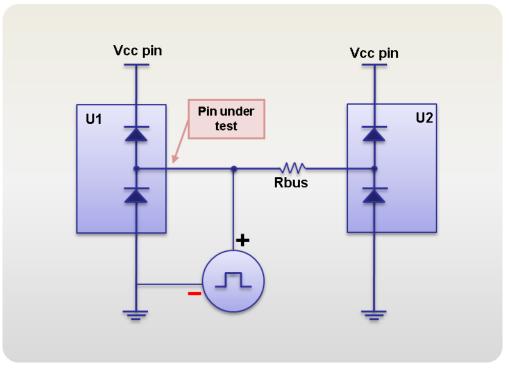

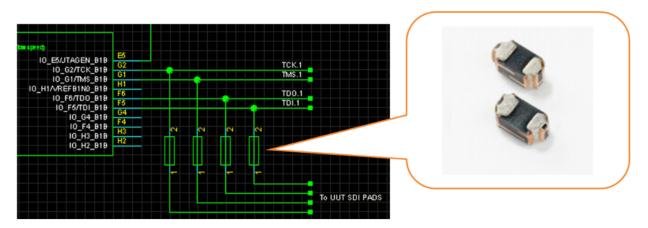

## 4.2.2 Junction scan

The Junction Scan is the testing technique that verifies the welding of the pin by measuring the component diodes (also called clamp diodes).

Where possible, in compliance with the electrical functionality of the board, it is advisable to provide separation resistors on the connection bus (called Rbus) between two components in order to be able to individually test the clamp diode avoiding the parallel effect.

Picture 25 - Junction Scan working principle

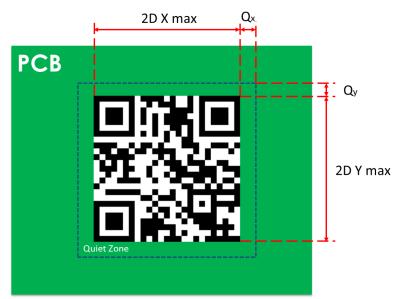

# 4.3 2D Code

The 2D Code is a two-dimensional bar code, i.e. matrix, composed of blacks modules arranged in a square pattern for storage of information such as:

- Serial Number

- Lot Number

- Manufacturing date

- ...

- Formats

-

• Dimensions

Picture 26 – QR code quotes

| No. | Parameter   | Dimension  |

|-----|-------------|------------|

| 1   | 2D Xmax     | 6 mm       |

| 2   | 2D Ymax     | 6 mm       |

| 3   | Minimum Qy  | 1 mm       |

| 4   | Minimum Qx  | 1 mm       |

| 5   | Minimum Dot | 150x150 µm |

Table 21 – QR code dimensions

# • Other characteristics

| No.        | Characteristic                                | Requirement     |

|------------|-----------------------------------------------|-----------------|

| 1          | Not covered by the overlying components       | MINIMUM         |

| 2          | Positioned at least on the primary test side  | MINIMUM (1)     |

| 3          | Positioned on both sides of the board         | RECOMMENDED (2) |

| 4          | Adjacent area free from other codes or labels | RECOMMENDED     |

| 5          | High contrast image compared to PCB           | MINIMUM         |

| (1)<br>(2) |                                               |                 |

Table 22 – 2D Code characteristics

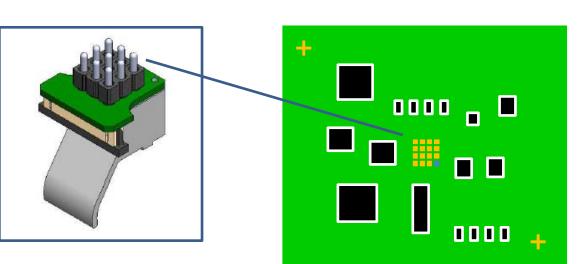

# 4.4 Multi Probe Unit (4080)

The Multi Probe Unit (MPU) is a mini flying fixture that can be installed on 4080 system:

- Top side on axes 1 and 4

- Bottom side axis 5 and 8

It can contact a designed pad array of the UUT and its able to perform tests such as:

- Functional Test

- Boundary Scan

- Power-On Test

The information in this chapter is useful for **electronic designer** and **PCB designer** involved in the following aspects:

- Mechanical design of pads and PCBs

- Physical constraints of the area surrounding the MPU

- Positioning of the pads on the UUT

- Electrical connections

Picture 27 – Multi Probe Probe Unit (MPU) and UUT Pod Area

Picture 28 - Example of contact on connector VS dedicated pads

# 4.4.1 Multi Probe on system top side

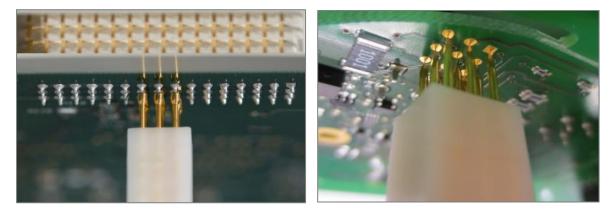

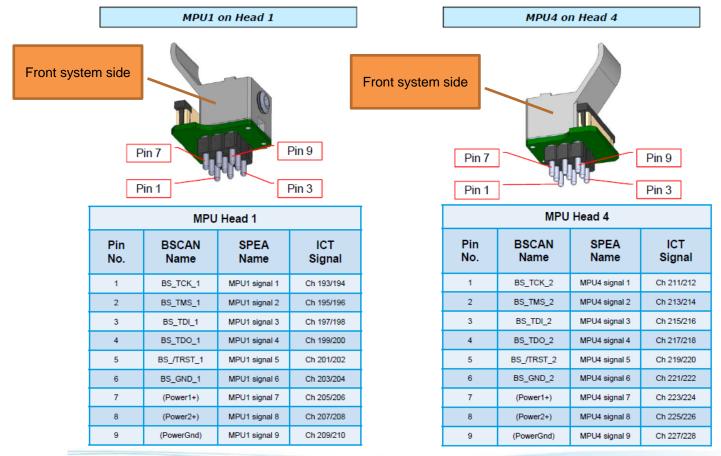

## 4.4.1.1 Head 1- 4 pinout

Picture 29 - Layout and pinout head 1 and 4

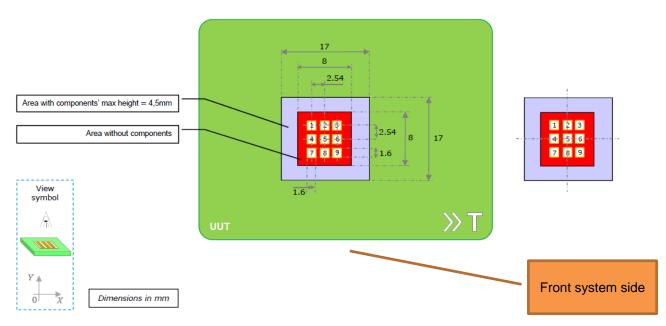

# 4.4.1.2 Pads design

Each MPU pad is composed by 9 square pads with the layout described below.

NOTE 1: MPU pads must be placed on the board side to be contacted by System Top Heads.

NOTE 2: MPU pads must be on the board PCB.

NOTE 3: MPU heads cannot rotate, so pads layout and board positioning inside the Flying Probe test area are related.

Picture 30 - Pad dimensions and layout of MPU's 1 and 4 top Side [dimensions in mm]

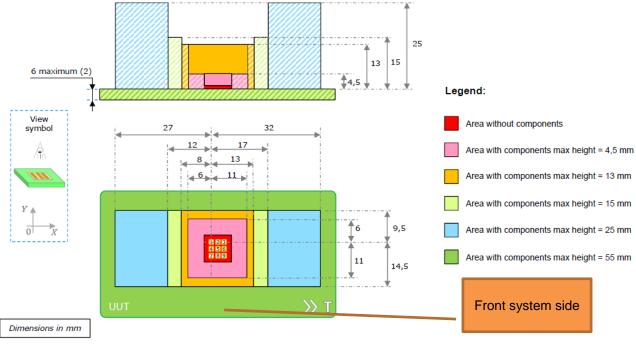

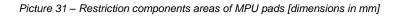

# 4.4.1.3 Components height

Around each MPU pad, components' height must respect conditions described below (1):

(1) When the MPU mechanism is not enabled it does not generate any restriction on components or on axes positioning capability (2) It's possible to use MPUs only if the UUT thickness is lower than 6mm

# 4.4.1.4 Working area

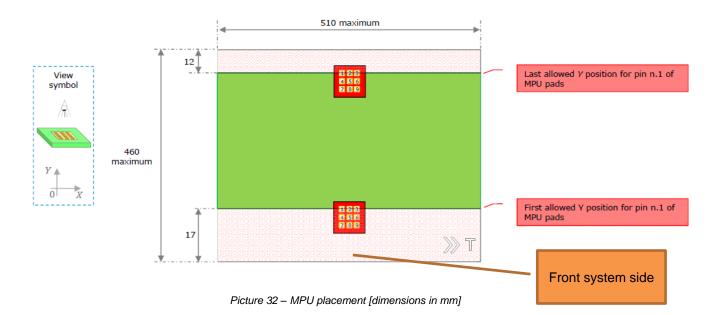

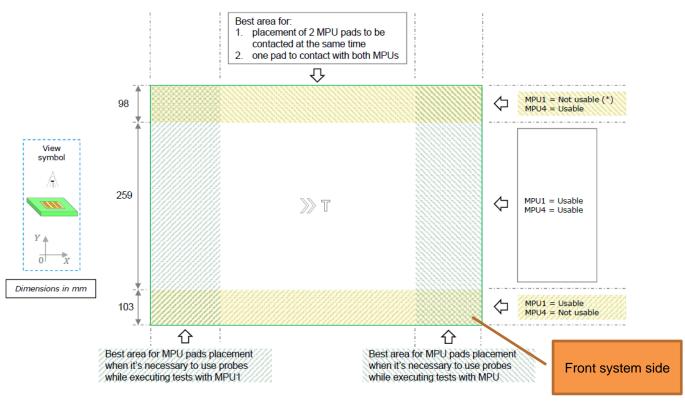

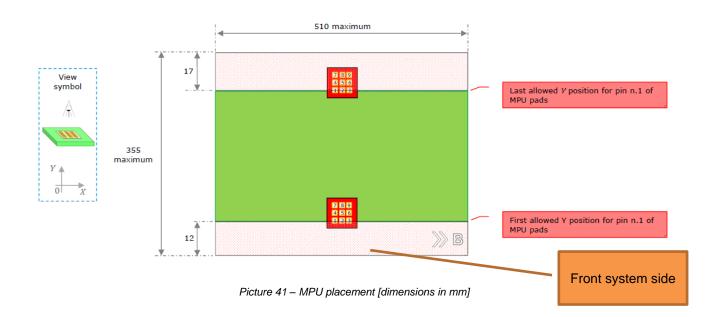

# 4.4.1.5 Placement inside UUT

(\*): MPU1 is not usable if UUT's depth is greater than 362mm (equal to 103mm+259mm).

# 4.4.1.6 MPU vs other test points

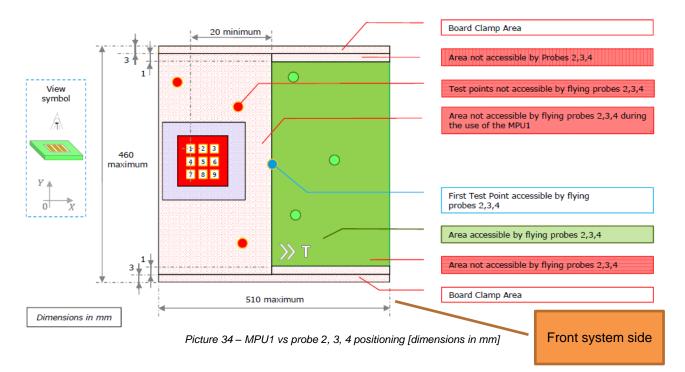

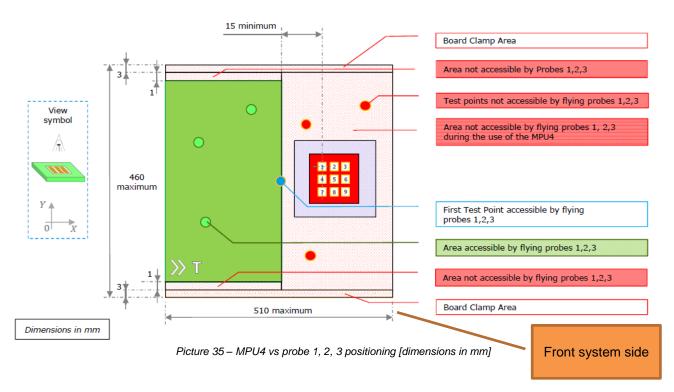

Test points closer than 20mm in X coordinate from pin 1 of MPU pod to be contacted with **MPU1** can not be reached by any probe. Test points further than 20mm can be contacted by other axes probes while **MPU1** is contacting the MPU pod (Picture 34).

Test points closer than 15mm in X coordinate from pin 1 of MPU pod to be contacted with **MPU4** can not be reached by any probe. Test points further than 20mm can be contacted by other axes probes while **MPU4** is contacting the MPU pod (Picture 35).

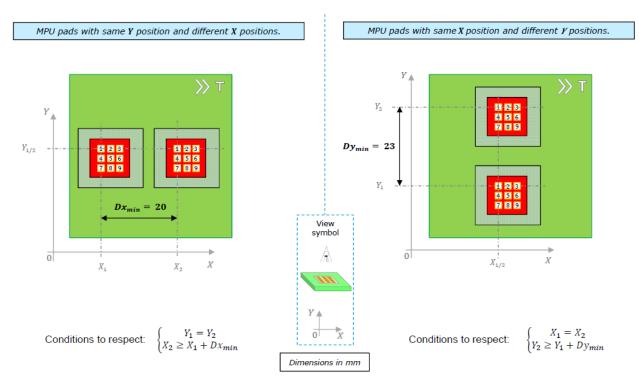

# 4.4.1.7 Simultaneously MPU positioning

To utilize no.2 MPU simultaneously below condition must be respected.

Picture 36 – Minimum distance between 2 pods per MPU on the same board [dimensions in mm]

# 4.4.1.8 MPU on panel of boards

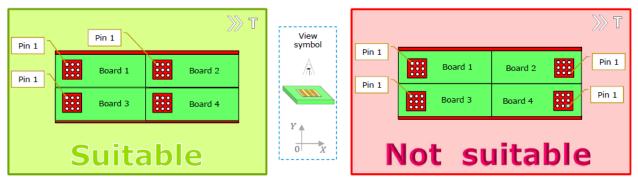

Positioning the MPU pods as shown in picture, the development of the program will be simplified.

The layout of this panel of boards makes simpler the development of the application and increases testability The layout of this panel of boards (boards rotated by 180°) makes necessary different cables and programming for MPU5 and MPU8

Picture 37 – Suitable and NOT suitable position on panel of boards [dimensions in mm]

#### 4.4.2 Multi Probe on system bottom side

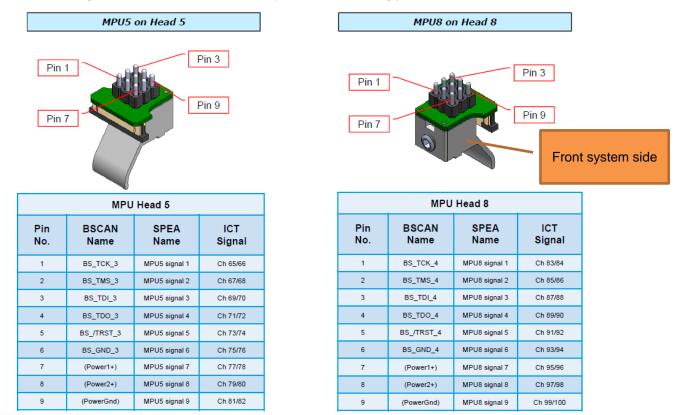

#### 4.4.2.1 Head 5-8 pinout

The MPU head is designed with 3 rows and 3 columns of pins with the following pinout:

Picture 38 – Layout and pinout head 1 and 4

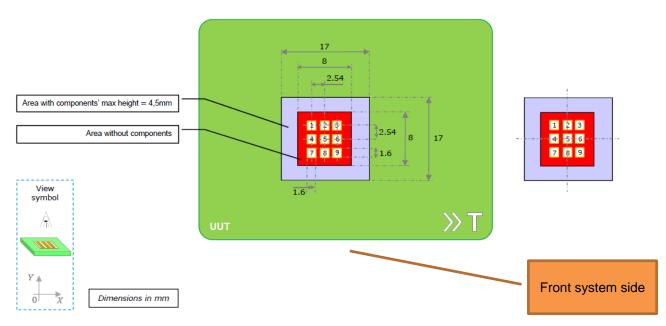

# 4.4.2.2 Pads design

Each MPU pad is composed by 9 square pads with the layout described below.

NOTE 1: MPU pads must be placed on the board side to be contacted by System Top Heads.

NOTE 2: MPU pads must be on the board PCB.

NOTE 3: MPU heads cannot rotate, so pads layout and board positioning inside the Flying Probe test area are related.

Picture 39 - Pad dimensions and layout of MPU's 1 and 4 top Side [dimensions in mm]

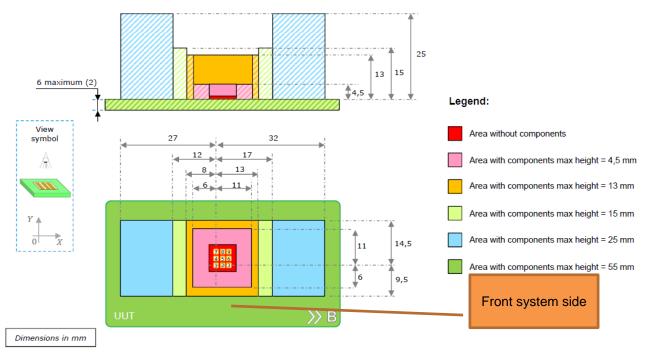

# 4.4.2.3 Components height

Around each MPU pad, components' height must respect conditions described below (1):

(1) When the MPU mechanism is not enabled it does not generate any restriction on components or on axes positioning capability (2) It's possible to use MPUs only if the UUT thickness is lower than 6mm

# 4.4.2.4 Working area

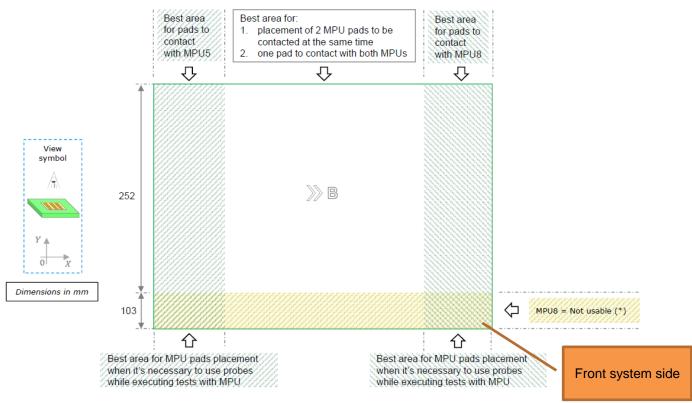

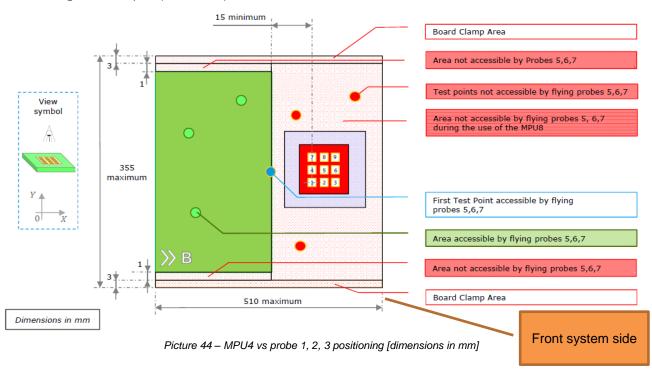

# 4.4.2.5 Placement inside UUT

(\*): MPU8 is not usable in this area if UUT's depth is greater than 252mm

# 4.4.2.6 MPU vs other test points

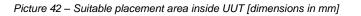

Test points closer than 20mm in X coordinate from pin 1 of MPU pod to be contacted with **MPU5** can not be reached by any probe. Test points further than 20mm can be contacted by other axes probes while **MPU5** is contacting the MPU pod (Picture 43).

Test points closer than 15mm in X coordinate from pin 1 of MPU pod to be contacted with **MPU8** can not be reached by any probe. Test points further than 20mm can be contacted by other axes probes while **MPU84** is contacting the MPU pod (Picture 44).

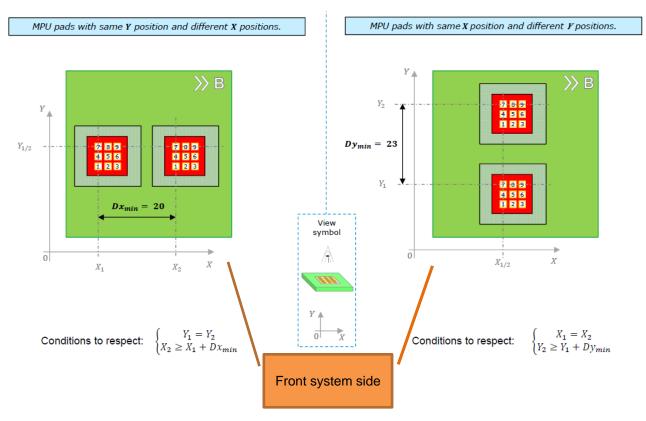

# 4.4.2.7 Simultaneously MPU positioning

To use both MPU simultaneously below condition must be respected.

Picture 45 - Minimum distance between 2 pods per MPU on the same board [dimensions in mm]

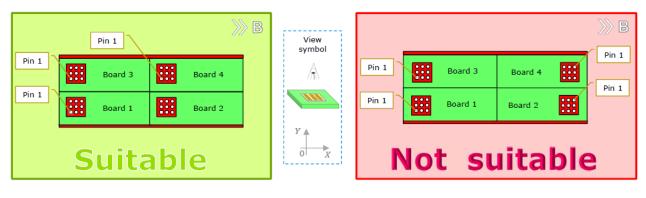

#### 4.4.2.8 MPU on panel of boards

Positioning the MPU pods as shown in picture, the development of the program will be simplified.

The layout of this panel of boards makes simpler the development of the application and increases testability The layout of this panel of boards (boards rotated by 180°) makes necessary different cables and programming for MPU5 and MPU8

Picture 46 – Suitable and NOT suitable position on panel of boards [dimensions in mm]

# 4.5 Measurement of light parameters

The Flying Probe of SPEA can measure the parameters of light emitted by the LEDs mounted on the UUT as:

- HSL

- RGB

- Lux

- Infrared

- Binning

- Cd

Picture 47 – Examples of LEDs

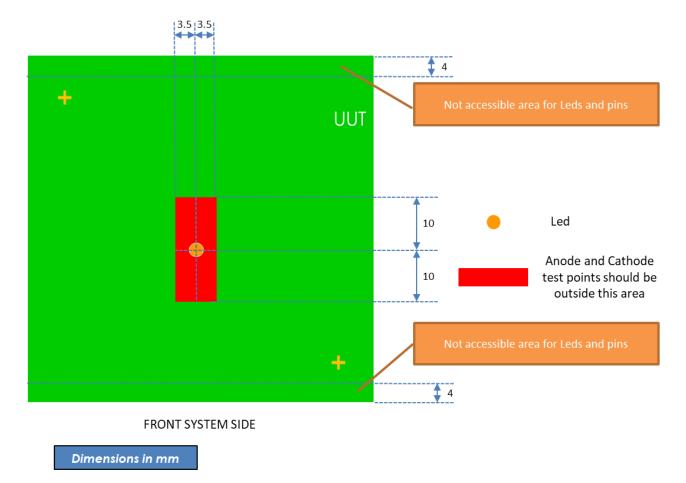

# 4.5.1 Pins accessibility

Anode and Cathode test points of each LED should be positioned out of the area showed on the picture 48.

Picture 48 – Anode and Cathode test point accessibility criteria (valid for LCS55)

NOTE: this information is valid for both top and bottom sides board design

# 4.5.2 Height of the components around the led

Around each LED, height of components must respect the conditions described on picture 49.

Picture 49 – Accessibility surrounded Led area (valid for LCS55)

#### Legend:

Note: all maximum heights are referred to LED's top face

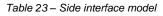

# 4.6 Side Device Interface (4080)

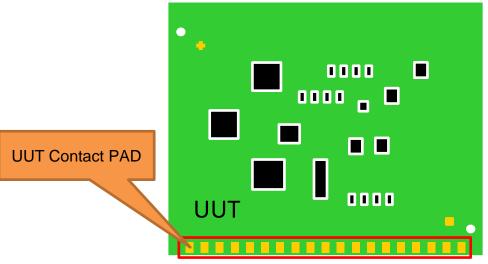

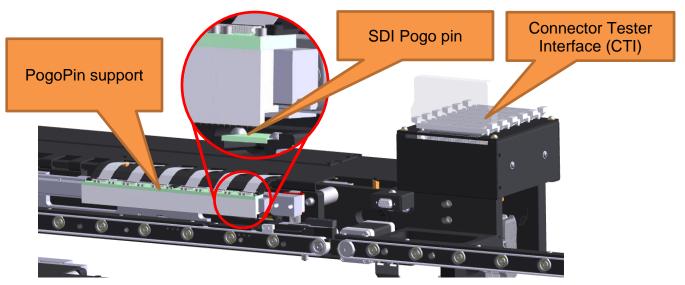

The Side Device Interface (SDI) is a contact unit which, through spring-loaded probes installed on the line clamping transports, allows signals to be applied to the UUT. Requires cards prepared with specially designed contact pads. Through the SDI you can perform tests such as:

- Functional test

- Power On test

- On-Board Programming

- Boundary Scan

The information in this chapter is useful for **electronic designers** and **PCB designers** involved in the following aspects:

- Mechanical design of the pads

- Electrical connections

- Electrical connections on the board

- Electrical constraints

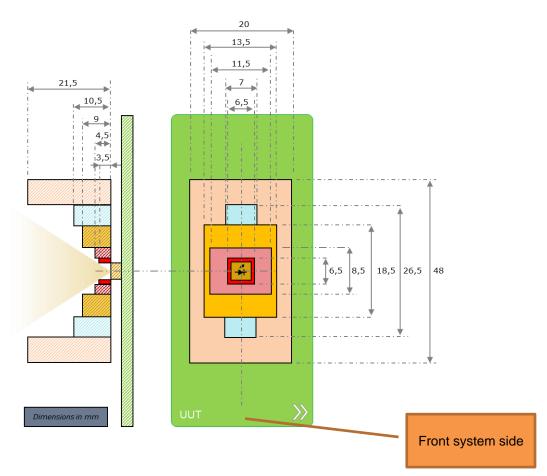

Picture 50 - Example of the SDI pod area on the UUT

Picture 51 – SDI mechanism and detail on Pogopin

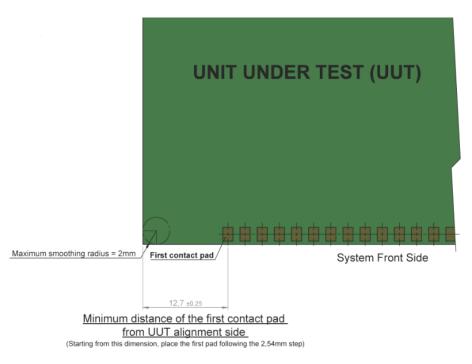

#### 4.6.1 Mechanical design of the pads

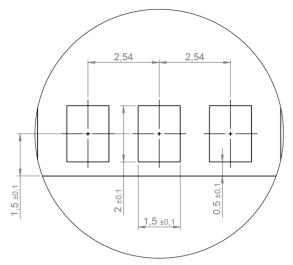

The picture below shows the information about the shape of the pads must have to be contactable through the SDI Pogo Pin:

Picture 52 – Pad dimensions for contact via SDI [dimensions in mm]

Picture 53 – Positioning of the first PAD for the contact of the Pogo Pin

| Model. | Max Pins | Side  |

|--------|----------|-------|

| SDI120 | 96       | Front |

# 4.6.2 Electrical connections

The connection of the SDI pins is completely free, in fact it is sufficient to connect the machine resource you need from the system interface to the SDI connectors.

Picture 54 – Example of connection between System Interface and SDI

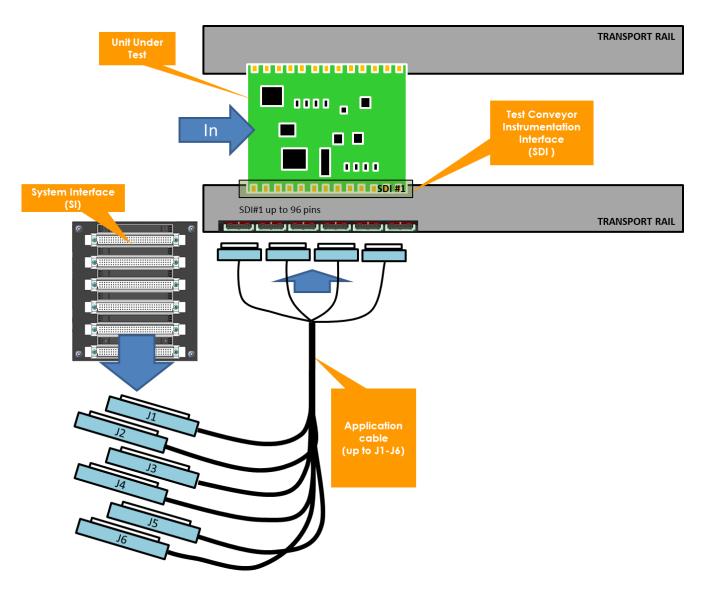

#### 4.6.3 Electrical connections on the board

If the board is framed, for example on a board panel, it is necessary to insert tracks from the board to the PAD through supports.

Picture 55 - Board support example

In the case of manual separation of the panel boards, the tracks must pass through the innermost layers of the PCB, in fact, passing them in the outer layers could lead to damage to the board during the division of the panel.

Each PogoPin is able to carry a maximum current of 1A, to force more current, it is necessary to create additional tracks and using more pads in parallel.

Picture 56 – Tip for separating the panel

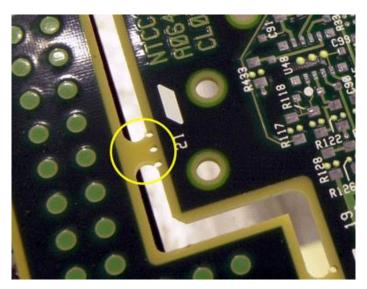

## 4.6.4 Electrical constraints

If the Pads are on the panel frame, you need to divide the tracks that lead to the PADs from the rest of the circuit, to avoid creating parasitic stubs.

An example of division of the tracks is to place fuses near the intersection of the net, and at the end of the test burn them.

Picture 58 – Example of circuit and fuses for the division of the net

# 4.7 Programmable components

The Flying Probe allows the programming of the programmable components during the execution of the test program.

Depending on the required programming signals and the necessary power supplies, programming can be carried out in different ways indicated in this chapter.

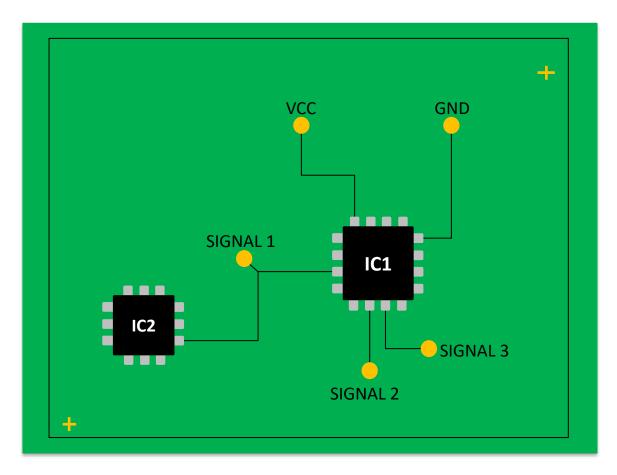

Picture 59 – Example of programmable component and relative accessibility

# 4.7.1 Pre-requisites for accessibility and constraints

To program a component it is suggested to take care of the following aspects:

- Total accessibility of all the points involved in the programming.

- Total accessibility of power nets from multiple points.

- Total accessibility of other signals needed for programming (constraints, pull-ups, pull-downs, ...)

- Total accessibility of all the signals necessary for disabling the component to be programmed or other programmable components (reset, ...)

- As far as possible, do not connect directly to VCC or GND the signals involved in the programming (restraints, reset, signals to force specific voltages ...).

- Provide, if possible, a status of the board that confirms the successful programming (LED, H / L signal, current absorption different from the unscheduled card, ...).

- Provide accessibility and the possibility to disable any oscillators.

#### 4.7.2 OTP components

In case of use of OTP components, it is recommended to install, for debugging operations, other programmable versions of the component (even if they have a different type of case) in which it is possible to perform more than one single programming.

#### 4.7.3 Programming of several components connected to each other

The simultaneous programming of different devices is not applicable if the components in question are shortcircuited.

Decoupling resistors on the programming bus must be provided between programmable components.

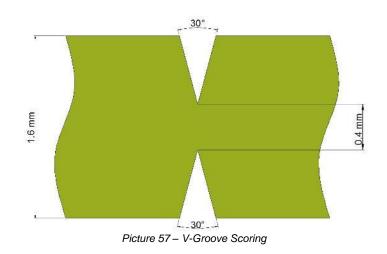

#### Picture 60 – Accessibility combinations

| Component<br>programming<br>signals | A<br>System<br>Int. | B<br>Cable | D<br>4-Axis<br>System | E<br>6-Axis<br>System | F<br>8-Axis<br>System | Signals<br>Programming<br>Access | Signals<br>Power Access |

|-------------------------------------|---------------------|------------|-----------------------|-----------------------|-----------------------|----------------------------------|-------------------------|

| Up to 2-Wires                       | -                   | -          | Х                     | -                     | -                     | Т                                | т                       |

| Up to 2-Wires                       | -                   | -          | -                     | Х                     | -                     | Т                                | T or B                  |

| Up to 2-Wires                       | -                   | -          | -                     | -                     | Х                     | T or B or C                      | T or B or C             |

| Up to 4-Wires (1)                   | х                   | Х          | Х                     | -                     | -                     | Т                                | Connector or B          |

| Up to 4-Wires                       | -                   | -          | -                     | Х                     | -                     | Т                                | В                       |

| Up to 4-Wires                       | -                   | -          | -                     | -                     | Х                     | T or B or C                      | T or B or C             |

| Up to 6-Wires (1)                   | х                   | Х          | Х                     | -                     | -                     | Connector                        | Connector               |

| Up to 6-Wires (1)                   | х                   | Х          | -                     | х                     | -                     | T + B                            | Connector               |

| Up to 6-Wires                       | -                   | -          | -                     | -                     | Х                     | T + B or C                       | T + B or C              |

| Up to 8-Wires (1)                   | х                   | х          | Х                     | -                     | -                     | Connector                        | Connector               |

| Up to 8-Wires (1)                   | х                   | Х          | -                     | х                     | -                     | Connector                        | Connector               |

| Up to 8-Wires                       | -                   | -          | -                     | -                     | Х                     | T + B or C                       | T + B or C              |

#### (1) Manual loading system

Table 24 – Recommended combinations in the accessibility of programming and power signals according to the system model